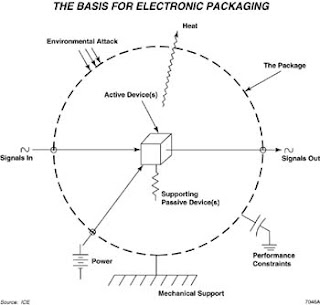

In order for the active device to function, it must be electrically connected to other devices-with physical assurance that the connections will be maintained. Further, the active device must be protected from attack by the environment. Finally, since the active device consumes power to perform its function, heat is generated. Since heat can shorten the life of active devices, a means must be provided to carry the heat away.

To provide these necessary functions of interconnection, physical support, environmental protection and heat dissipation, the active device must be surrounded by or encased in a package. An illustrarion of this concept is presented in Figure 1. Packages may be simple or they maybe complex-depending on the nature of the device, the system of which it is a part and the environment in which the device must operate.

The very surrounding of the active device with protective material, however, can degrade the performance if the device, increase its physical size and weight, make testing the device more difficult and decrease reliability. Moreover, the art of

making the electronic package incure costs-which may be far higher than the cost of the active device itself. Thus, the art of providing an effective electronic package becomes a complex balence of providing desired functions against constraints which may interact among themselves as even further constraints.

As a practical matter, the IC manufacturer must decide whether to package a given IC in one or more standard packages (nesessary for merchant sales) or develop one unique to its needs (giving it a systems advantage over its competitors). We will confine our discusions to "standard" types, however.